(1) ADG: Automotive and Discretes Group - ASD: Application Specific Device – IPAD™: Integrated Passive and Active Devices

# PCN Product/Process Change Notification

Additional assembly and test line qualification for FERD diodes housed in DPAK package

| Notification number:                  | ADG-DIS/18/10745 | Issue Date           | 19/02/2018 |

|---------------------------------------|------------------|----------------------|------------|

| Issued by                             | Aline AUGIS      |                      |            |

| Product series affected by the change |                  | FERDxxxSB-TR         |            |

| Type of change                        |                  | Back-end realization |            |

#### Description of the change

Qualification of an additional back-end subcontractor located in China (location B) for the assembly and test and finishing of FERD products in DPAK as a double sourcing of location A (China).

Location B is already a major production site for ST, including Power Schottky and ultrafast diodes technologies.

#### Reason for change

STMicroelectronics investment on FERD capacity increase.

| Former versus changed product: | The changed products do not present modified electrical,<br>dimensional or thermal parameters, leaving unchanged the<br>current information published in the product datasheet. |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                | The Moisture Sensitivity Level of the part (according to the IPC/JEDEC JSTD-020D standard) remains unchanged.                                                                   |

|                                | The footprint recommended by ST remains the same.                                                                                                                               |

|                                | There is no change in the packing modes and the standard delivery quantities either.                                                                                            |

|                                | The products remain in full compliance with the ST ECOPACK®2 grade ("halogen-free").                                                                                            |

The current production will still run.

Shipments will be done from both former and new assembly locations.

#### STMicroelectronics ADG - ASD & IPAD<sup>™</sup> Division<sup>1</sup> BU Rectifiers

(1) ADG: Automotive and Discretes Group - ASD: Application Specific Device – IPAD™: Integrated Passive and Active Devices

#### Marking and traceability:

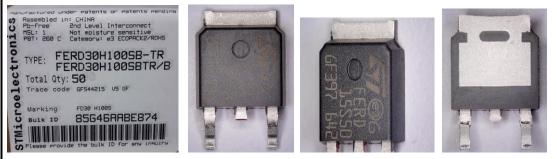

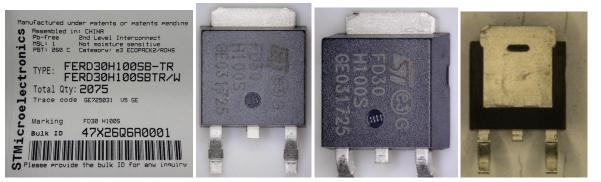

The die marking is the same between plant A and B. Traceability of the BE plant will be ensured by an internal codification (Finished Good) and by trace code (die marking and on the carton box label). The first two digits of the trace code indicate the back end plant provenance.

#### LOCATION A

#### LOCATION B

| Commercial Product | LOCATION A       | LOCATION B       | MARKING    |

|--------------------|------------------|------------------|------------|

|                    | Finished Good    | Finished Good    |            |

| FERD15S50SB-TR     | FERD15S50SBTR/B  | FERD15S50SBTR/W  | FERD 15S50 |

| FERD20H100SB-TR    | FERD20H100SBTR/B | FERD20H100SBTR/W | FD20 H100S |

| FERD20S100SB-TR    | FERD20S100SBTR/B | FERD20S100SBTR/W | FD20 S100S |

| FERD30H100SB-TR    | FERD30H100SBTR/B | FERD30H100SBTR/W | FD30 H100S |

| Qualification complete date | Week 48/2017 |

|-----------------------------|--------------|

|-----------------------------|--------------|

#### Forecasted sample availability

| Product family | Sub-family | Commercial part<br>Number | Availability date |

|----------------|------------|---------------------------|-------------------|

| Rectifiers     | DPAK       | FERD15S50SB-TR            | W05/2018          |

| Rectifiers     | DPAK       | FERD20H100SB-TR           | W05/2018          |

| Rectifiers     | DPAK       | FERD20S100SB-TR           | W05/2018          |

| Rectifiers     | DPAK       | FERD30H100SB-TR           | W05/2018          |

#### STMicroelectronics ADG - ASD & IPAD<sup>™</sup> Division<sup>1</sup> BU Rectifiers

(1) ADG: Automotive and Discretes Group - ASD: Application Specific Device – IPAD™: Integrated Passive and Active Devices

| Change implementation schedule                                                                                                                                                                                             |           |                  |                           |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|------------------|---------------------------|--|

| Sales types                                                                                                                                                                                                                | Estimated | production start | Estimated first shipments |  |

| FERDxxxSB-TR                                                                                                                                                                                                               | Wee       | k 51/2017        | Week 21/2018              |  |

| Comments:                                                                                                                                                                                                                  |           |                  |                           |  |

| Customer's feedback                                                                                                                                                                                                        |           |                  |                           |  |

| Please contact your local ST sales representative or quality contact for requests concerning this change notification.                                                                                                     |           |                  |                           |  |

| Absence of acknowledgement of this PCN within 30 days of receipt will constitute acceptance of the change<br>Absence of additional response within 90 days of receipt of this PCN will constitute acceptance of the change |           |                  |                           |  |

| Qualification program and results                                                                                                                                                                                          |           | 17105QRP Attache | d                         |  |

# **Reliability Evaluation Report**

Qualification of FERDxxxSB-TR

at additional subcontractor in China 994X

|                     | General Information |

|---------------------|---------------------|

| Product Line        | RECTIFIERS          |

| Product Description | AFER diode          |

|                     | FERD15S50SB-TR      |

| Product             | FERD20H100SB-TR     |

| Product             | FERD20S100SB-TR     |

|                     | FERD30H100SB-TR     |

| Product Group       | ADG                 |

| Product division    | ASD&IPAD            |

| Package             | DPAK                |

| Maturity level step | Qualified           |

|                     |                     |

|                             | Locations                  |

|-----------------------------|----------------------------|

| Wafer fab                   | ST Catania (ITALY)         |

| Electrical Wafer<br>Sorting | ST SINGAPORE               |

| Assembly plant              | Subcontractor 994X (CHINA) |

| Reliability Lab             | ST Tours (FRANCE)          |

| Reliability<br>assessment   | Pass                       |

#### DOCUMENT INFORMATION

| Versi | on Date     | Pages | Prepared by     | Approved by     | Comment         |

|-------|-------------|-------|-----------------|-----------------|-----------------|

| 0.1   | 19-Oct-2017 | 7     | Isabelle BALLON | Julien MICHELON | Initial release |

This report does not imply for STMicroelectronics expressly or implicitly any contractual obligations other than as set forth in STMicroelectronics general terms and conditions of Sale. This report and its contents shall not be disclosed to a third party without previous written agreement from STMicroelectronics.

Note: This report is a summary of the reliability trials performed in good faith by STMicroelectronics in order to evaluate the potential reliability risks during the product life using a set of defined test methods.

### TABLE OF CONTENTS

| 1<br>2 |       | CABLE AND REFERENCE DOCUMENTS |   |

|--------|-------|-------------------------------|---|

| 2      |       | BILITY EVALUATION OVERVIEW    |   |

| •      | 3.1   | OBJECTIVES                    |   |

|        | 3.2   | Conclusion                    |   |

| 4      | DEVIC | CE CHARACTERISTICS            |   |

|        | 4.1   | DEVICE DESCRIPTION            |   |

|        | 4.2   | CONSTRUCTION NOTE             |   |

| 5      | TESTS | RESULTS SUMMARY               |   |

|        | 5.1   | TEST VEHICLES                 |   |

|        |       | TEST PLAN AND RESULTS SUMMARY |   |

| 6      | ANNE  | XES                           |   |

|        | 6.1   | TESTS DESCRIPTION             | 7 |

# **<u>1</u>** APPLICABLE AND REFERENCE DOCUMENTS

| Document reference | Short description                                                         |

|--------------------|---------------------------------------------------------------------------|

| JESD 47            | Stress-Test-Driven Qualification of Integrated Circuits                   |

| JESD 94            | Application specific qualification using knowledge based test methodology |

| JESD 22            | Reliability test methods for packaged devices                             |

### 2 GLOSSARY

| SS    | Sample Size                             |

|-------|-----------------------------------------|

| PC    | Pre-conditioning                        |

| HTRB  | High Temperature Reverse Bias           |

| тс    | Temperature Cycling                     |

| тнв   | Thermal Humidity Bias                   |

| UHAST | Unbiased Highly Accelerated Stress Test |

| SD    | Solderability                           |

| RSH   | Resistance to Soldering Heat            |

| DBT   | Dead Bug Test                           |

| GD    | Generic Data                            |

### 3 RELIABILITY EVALUATION OVERVIEW

### 3.1 **Objectives**

The objective of this report is to qualify Field-Effect Rectifier Diodes, FERDxxxSB-TR mounted in DPAK package at additional subcontractor in China (994X).

| Product                                                                 | Package | Assembly location          |

|-------------------------------------------------------------------------|---------|----------------------------|

| FERD15S50SB-TR<br>FERD20H100SB-TR<br>FERD20S100SB-TR<br>FERD30H100SB-TR | DPAK    | Subcontractor 994X (China) |

The reliability test methodology used follows the JESD47: « Stress Test Driven Qualification Methodology » guidelines. The following reliability tests ensuing are:

- TC to ensure the mechanical robustness of the products.

- HTRB to evaluate the risk of contamination from the resin and the assembly process versus the die layout sensitivity.

- THB, UHAST to check the robustness to corrosion and the good package hermeticity.

- RSH, Solderability and DBT to check compatibility of package with customer assembly.

The qualification plan is based on similarity methodology. See 5.1 "comments" for more details.

#### 3.2 Conclusion

Qualification Plan requirements have been fulfilled without exception. Reliability tests have shown that the devices behave correctly against environmental tests (no failure). Moreover, the stability of electrical parameters during the accelerated tests demonstrates the robustness of the products and safe operation, which is consequently expected during their lifetime.

# **<u>4</u> DEVICE CHARACTERISTICS**

### 4.1 **Devices description**

Refer products datasheets.

### 4.2 Construction note

See referenced Product Baseline for detailed information.

|                                           | FERDxxxSB-TR                          |  |  |

|-------------------------------------------|---------------------------------------|--|--|

| Wafer/Die fab. information                |                                       |  |  |

| Wafer fab manufacturing location          | ST CATANIA – ITALY                    |  |  |

| Technology / Process family               | AFER                                  |  |  |

| Wafer Testing (EWS) information           |                                       |  |  |

| Electrical testing manufacturing location | ST SINGAPORE                          |  |  |

| Assembly information                      |                                       |  |  |

| Assembly site                             | Subcontractor 994X (China)            |  |  |

| Package description                       | DPAK                                  |  |  |

| Molding compound                          | ECOPACK <sup>®</sup> molding compound |  |  |

| Lead finishing material                   | Tin (Sn)                              |  |  |

| Final testing information                 |                                       |  |  |

| Testing location                          | Subcontractor 994X (China)            |  |  |

### 5 TESTS RESULTS SUMMARY

## 5.1 <u>Test vehicles</u>

|       | Test vehicles for FERDxxxSB-TR |         |                            |                                                            |  |

|-------|--------------------------------|---------|----------------------------|------------------------------------------------------------|--|

| Lot # | Commercial<br>product          | Package | Assy / Test location       | Comments                                                   |  |

| L1    | FERD30H100SB-TR                | DPAK    | Subcontractor 994X ((hina) | Similar die technology (Larger die) with<br>higher voltage |  |

Detailed results in below chapter will refer to P/N and Lot #.

### 5.2 Test plan and results summary

| FERDxxxSB-TR qualification test plan and results |         |                             |                                                              |          |      |                                                                  |

|--------------------------------------------------|---------|-----------------------------|--------------------------------------------------------------|----------|------|------------------------------------------------------------------|

| Test                                             | РС      | Std ref.                    | Conditions                                                   | Steps /  | SS . | Failure/SS                                                       |

| rest                                             | **      | oturen                      | Conditions                                                   | Duration |      | L1                                                               |

| Die oriente                                      | d Test  | s                           |                                                              | 1        |      |                                                                  |

| HTRB                                             | N       | JESD22<br>A-108             | VR=0.8xVrrm<br>Ta=(*)                                        | 1Khrs    | 77   | 0/77                                                             |

| Package o                                        | riented | Tests                       |                                                              |          |      |                                                                  |

| тс                                               | Y       | JESD22<br>A-104             | -65/+150°C<br>2cy/h                                          | 500cy    | 77   | 0/77                                                             |

| ТНВ                                              | Y       | JESD22<br>A-101             | 85°C; 85% RH<br>VR=0.8xVRRM<br>(limited to 100V)             | 1Khrs    | 77   | 0/77                                                             |

| UHAST                                            | Y       | JESD22<br>A-118             | 130°C 85% RH                                                 | 96hrs    | 77   | 0/77                                                             |

|                                                  |         |                             | Dry ageing<br>SnPb bath 220°C                                | -        | 10   | 0/10                                                             |

| SD                                               | Y       | JESD22                      | Wet ageing<br>SnPb bath 220°C                                | -        | 10   | 0/10                                                             |

| 30                                               | T       | B-102                       | Dry ageing<br>SnAgCu bath 245°C                              | -        | 10   | 0/10                                                             |

|                                                  |         |                             | Wet ageing<br>SnAgCu bath 245°C                              | -        | 10   | 0/10                                                             |

| RSH                                              | Y       | JESD22<br>A-111             | 85°C/85%RH<br>Ageing 168hrs<br>10sec solder dipping<br>260°C | -        | -    | Not applicable acc.<br>JESD22A-111 vs<br>package/die paddle size |

| DBT                                              | Y       | DM00112629<br>(ST internal) | IR reflow<br>after flux deposition                           | -        | 30   | 0/30                                                             |

Note: Whiskers positive data available from monitoring only.

\* Maximal available temperature preventing from thermal runaway corresponding to Ta =120°C, Tj~125°C

\*\* All package-oriented tests are submitted to preconditioning PC before test.

# <u>6</u> <u>ANNEXES</u>

# 6.1 **Tests Description**

| Test name                                              | Description                                                                                                                                                                                                                                     | Purpose                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|--------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Die Oriented                                           |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>HTRB</b><br>High Temperature<br>Reverse Bias        | The device is stressed in static configuration,<br>trying to satisfy as much as possible the<br>following conditions:<br>low power dissipation;<br>max. supply voltage compatible with diffusion<br>process and internal circuitry limitations; | To determine the effects of bias conditions and<br>temperature on solid state devices over time. It<br>simulates the devices operating condition in an<br>accelerated way.<br>To maximize the electrical field across either<br>reverse-biased junctions or dielectric layers, in<br>order to investigate the failure modes linked to<br>mobile contamination, oxide ageing, layout<br>sensitivity to surface effects.                                                        |

| Package Oriented                                       |                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| <b>THB</b><br>Temperature<br>Humidity Bias             | The device is biased in static configuration<br>minimizing its internal power dissipation, and<br>stored at controlled conditions of ambient<br>temperature and relative humidity.                                                              | To evaluate the package moisture resistance with electrical field applied, both electrolytic and galvanic corrosion are put in evidence.                                                                                                                                                                                                                                                                                                                                      |

| <b>TC</b><br>Temperature Cycling                       | The device is submitted to cycled temperature excursions, between a hot and a cold chamber in air atmosphere.                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| UHAST<br>Unbiased Highly<br>Accelerated Stress<br>Test | The device is stored in saturated steam, at fixed<br>and controlled conditions of pressure and<br>temperature.                                                                                                                                  | To investigate corrosion phenomena affecting die<br>or package materials, related to chemical<br>contamination and package hermeticity.                                                                                                                                                                                                                                                                                                                                       |

| <b>SD</b><br>Solderability                             | Wet/Dry ageing + dipping in a solder bath.<br>Assessment by visual inspection of the leads.                                                                                                                                                     | To check package ability to be soldered with no<br>difficulty. To simulate whether the packaging<br>materials and processes used during the<br>manufacturing operations process produce a<br>component that can be successfully soldered to<br>the next level assembly at customer using tin lead<br>eutectic solder. A preconditioning test is included<br>in this test method, which degrades the<br>termination finish to provide a guard band against<br>marginal finish. |

| <b>RSH</b><br>Resistance to<br>Soldering Heat          | Package is dipped by the leads in a solder bath after an initial wet ageing.                                                                                                                                                                    | To simulate wave soldering process and verify that package will not be thermally damaged during this step.                                                                                                                                                                                                                                                                                                                                                                    |

| <b>DBT</b><br>Dead Bug Test                            | Leads are covered with soldering flux and are<br>submitted to IR reflow. Assessment by visual<br>inspection of the leads                                                                                                                        | To ensure good wettability of the leads                                                                                                                                                                                                                                                                                                                                                                                                                                       |